# **ADQ3-FWPD** Datasheet

The ADQ3-FWPD is a real-time pulse detection and pulse analysis FPGA firmware for the high-end ADQ3-series digitizers. ADQ3-FWPD adds pulse attribute calculations to the standard firmware FWDAQ.

# **Ordering information**

- Firmware option FWPD for ADQ3-series of digitizer, order code ADQ3-FWPD.

- FWPD combined with firmware development kit, ADQ3-DEVPD (available 2024)

# Compatible hardware models

- ADQ30 single-channel mode

- ADQ32 single- and dual-channel modes

- ADQ32-PDRX combined channels and dual-channel mode (not combined)

- ADQ33 dual-channel mode

- ADQ33-PDRX combined channels and dual-channel mode (not combined)

- ADQ35 single- and dual-channel mode

- ADQ36 in dual- and quad-channels modes

# **TELEDYNE** SP DEVICES Everywhere**you**look

### 1 ADQ3-FWPD INTRODUCTION

#### 1.1 Features

- Compliant with features of FWDAQ

- Frame pulses using trigger blocking

- Detect pulses using level trigger

- Correct baseline using Digital baseline Stabilizer (DBS)

- Timestamp for pulse time determination

- Daisy-chain trigger distribution concept for large arrays of detectors

- Data rate reduction in the FPGA of the digitizer by computing attributes of pulses

- Data and attributes transferred as separate channels for flexible selection of operating mode

- Pulse attribute calculations:

- o Area (sum)

- Full width half max (FWHM)

- o Time of pulse peak

- Maximum pulse amplitude

- Open FPGA allows for customization of attributes

#### 1.2 Applications

- Time-of-flight mass spectrometry

- Lidar

- Neutron time-of-flight

- High energy physics

- Other types of pulse detection

#### 1.3 Advantages

- Efficient implementation of pulse detection and analysis in the FPGA off-loading the PC

- Optimized for real-time processing and high data throughput

- Teledyne SP Devices' design services are available for fast integration to reduce time-tomarket

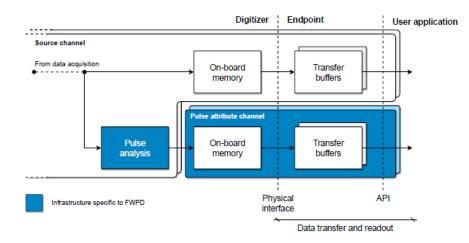

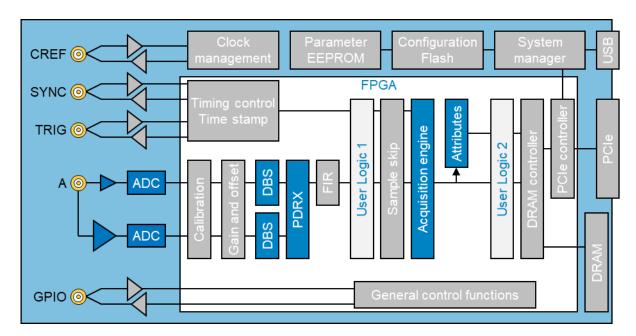

#### 2 BLOCK DIAGRAM

Figure 1 Block diagram of FWPD. FWPD adds attributes computations and attributes channels to the functions in standard firmware FWDAQ.

## **3** PULSE DETECTION AND ANALYSIS – PRINCIPLE OF OPERATION<sup>1</sup>

### 3.1 DBS – Digital Baseline Stabilizer

The DBS analyses the signal and subtracts the DC-offset. This creates a stable reference point for computing pulse-related parameters. The DBS actively compensates for slow baseline shifts such as temperature variations, supply voltage drift and aging, and stabilizes the baseline to a level corresponding to 22-bit precision. The DBS also compensates for pattern noise in interleaved ADCs.

### 3.2 General-purpose FIR filter

The general-purpose FIR filter enables the suppression of noise in a certain frequency band. The FIR filter is user-controlled so that it can be optimized for the specific application/system.

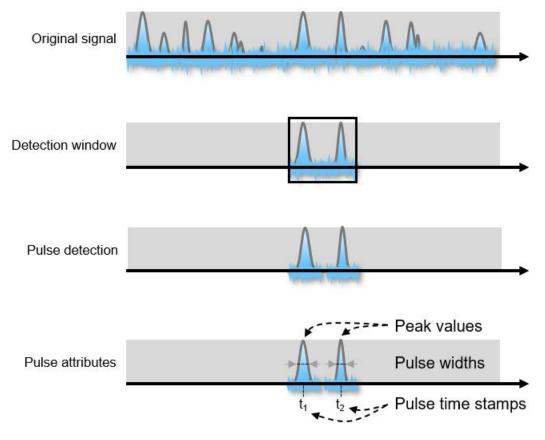

#### 3.3 Detection window

The detection window defines where to search for pulses. It is controlled by an event (trigger) and a length parameter. The detection window is comparable to the term "record" in the standard acquisition mode.

#### 3.4 Pulse detection

Pulse detection is handled by level triggering. The start of a pulse occurs when the signal level is passing a level and end of a pulse occurs when the signal is passing the same level from the opposite direction. The direction is depending on the polarity of the pulse.<sup>2</sup> A leading-edge window and a trailing-edge window define additional samples that belong to the pulse.

#### 3.5 Pulse attributes analysis

A set of standard attributes is calculated for each pulse in FWPD. The attributes can be replaced by custom attributes using the open FPGA.<sup>3</sup>

The 21-2539 user guide of ADQ3 digitizers contains a detailed definition of how the attributes are computed.

- Time of pulse peak

- Area (sum) of pulse

- Full width at half maximum (FWHM)

- Peak amplitude

The attributes are sent to the host PC on a separate attributes channel. The digital output of the board has twice as many channels as analog inputs, data, and attributes per channel.

<sup>&</sup>lt;sup>1</sup> All features in this section except for the computation of attributes and the attributes data channel are available in standard firmware FWDAQ.

<sup>&</sup>lt;sup>2</sup> The polarity of the pulses is set by the user. The FWPD can only handle one polarity per channel.

<sup>&</sup>lt;sup>3</sup> Open FPGA is accessed through the development kit with order code DEVPD. The DEVPD is available in 2024. Please contact Teledyne SP Devices for more information.

# TELEDYNE SP DEVICES Everywhereyoulook™

## 4 SYSTEM DESIGN USING FWPD

#### 4.1 Fundamental observations

FWPD is used in measurement systems where detectors and the digitizer operate in a real-time. The data, on the other hand, is analyzed on a PC, which is not real-time controlled. FWPD is designed to handle the transition between the real-time domain into the PC in a safe way.

#### 4.2 System design optimization - open FPGA and streaming to CPU and GPU

High-performance data acquisition systems require high-speed real-time analysis. The ADQ3-series offers a variety of options for efficient system design:

The FWPD firmware implements the most demanding core processing inside the FPGA. Data from the processing is streamed to a PC using the high-speed streaming interface.

The streaming is done in parallel with the recording without introducing any dead-time.

See the ADQ3-series user guide for instructions on how to tune parameters for optimal performance.<sup>4</sup>

#### 4.3 Large arrays of detectors

Use the Daisy-chain trigger distribution for synchronization of large arrays.

#### 4.4 Scheduling for high performance and data safety

FWPD is designed for systems with data-driven operation. The dataflow is driven by pulse activity. The ADQ3-series digitizer contains a large FIFO to smoothen the data flow. The user must ensure that all data transfer and processing is fast enough to handle the average data rate.

FWPD is designed to operate constantly over a long time in order to maximize performance. It contains multiple features to support the necessary data transfer and processing:

- 1. There is an onboard FIFO to manage unexpected interrupts in the PCIe data transport.

- 2. There is a controlled data discard in case of an overflow due to interrupts anywhere in the processing chain.

- 3. There is an auto-recover and resynchronization feature in case of lost data. This is useful for very long measurement operations. In case of an unexpected interrupt in the data transport which cannot be handled by the FIFO, the FWPD firmware maintains the grid established by the trigger source. It is not necessary to restart the system to continue the measurement.

- 4. The data readout is thread-safe and multiple threads can operate on the data. This increases the processing capacity of the system.

<sup>&</sup>lt;sup>4</sup> ADQ3-series user guide with document number 21-2539 can be downloaded from www.spdevices.com

### 5 TECHNICAL DATA

#### **Table 1 Pulse detection**

| Parameter                                      | Description                                                     | Limitation                                 |

|------------------------------------------------|-----------------------------------------------------------------|--------------------------------------------|

| Pulse spacing                                  | Distance between two consecutive pulse peaks                    | Min 2 samples                              |

| Pulse rate                                     | Maximum sustained rate for ADQ32, ADQ35, ADQ36                  | Max 312.5 Mpulses per<br>second⁵           |

| Pulse rate                                     | Maximum sustained rate for ADQ30, ADQ33                         | Max 125 Mpulses per<br>second <sup>5</sup> |

| Burst length                                   | Burst of pulses exceeding average long-<br>term pulse rate      | Max 256 pulses                             |

| Burst length for<br>ADQ35 in 1-channel<br>mode | Additional burst length requirement for ADQ35 in 1 channel mode | Max 8 pulses per set of 32 samples         |

#### **Table 2 Attributes**

| Attribute  | Description             | Size<br>[bytes] |

|------------|-------------------------|-----------------|

| Time       | Time of peak value      | 4               |

| Area       | Area (sum) of pulse     | 4               |

| FWHM       | Full width half max     | 2               |

| Peak value | Value of largest sample | 2               |

| Reserved   | Reserved                | 4               |

<sup>&</sup>lt;sup>5</sup> This is the capacity of the analysis firmware. Note that there is also a data transfer limit over PCIe of the hardware.

#### Table 3 Limitations on computations of attributes

| Model      | Channels | Sampling | ampling FWHM max |           | Area computation     |                      |

|------------|----------|----------|------------------|-----------|----------------------|----------------------|

|            |          | rate     | Time             | Length    | Max LEW <sup>6</sup> | Max TEW <sup>7</sup> |

|            |          | [GHz]    | [us]             | [samples] | [Samples]            | [Samples]            |

| ADQ30      | 1        | 1        | 4.1              | 4096      | 64                   | 64                   |

| ADQ32      | 2        | 2.5      | 3. 3             | 8192      | 64                   | 64                   |

| ADQ32      | 1        | 5        | 3.3              | 16384     | 64                   | 64                   |

| ADQ32-PDRX | 1        | 2.5      | 3.3              | 8192      | 64                   | 64                   |

| ADQ33      | 2        | 2.5      | 4.1              | 4096      | 64                   | 64                   |

| ADQ35      | 2        | 5        | 3.3              | 16384     | 64                   | 64                   |

| ADQ35      | 1        | 10       | 3.3              | 32768     | 64                   | 64                   |

| ADQ35-PDRX | 1        | 5        | 3.3              | 16384     | 64                   | 64                   |

| ADQ36      | 4        | 2.5      | 3.3              | 8192      | 64                   | 64                   |

| ADQ36      | 2        | 5        | 3.3              | 16384     | 64                   | 64                   |

#### **Table 4 Software support**

| Parameter                     | Value            |

|-------------------------------|------------------|

| Operating system <sup>8</sup> | Windows / Linux  |

| GUI                           | Digitizer Studio |

| Example code                  | C, Python        |

| API                           | C / C++          |

<sup>&</sup>lt;sup>6</sup> LEW is leading edge window, that is, the number of samples before passing the threshold at the start of the pulse.

<sup>&</sup>lt;sup>7</sup> TEW is trailing edge window, that is the number of samples after passing the threshold at the end of the pulse.

<sup>&</sup>lt;sup>8</sup> See 15-1494 Operating system support for a detailed listing of supported distributions.

### Table 5 Data transfer rate

| Mode                               | Description                        | Data set per trigger <sup>9</sup>             |

|------------------------------------|------------------------------------|-----------------------------------------------|

| Continuous recording <sup>10</sup> | Continuous recording of raw data   | PCIe transfer rate limits the                 |

| of original signal                 | from original signal               | recording                                     |

| Detection window                   | All data within a detection window | Record length + header <sup>11</sup>          |

| /record <sup>10</sup>              | is recorded as one record          |                                               |

| Pulse detection / zero             | Samples which belong to pulses are | Average number of pulses *                    |

| suppression <sup>10</sup>          | recorded                           | (header <sup>11</sup> + average pulse length) |

| Pulse attributes <sup>12</sup>     | Computed attributes of pulses      | Header <sup>11</sup> + 16 bytes *             |

|                                    |                                    | average number of pulses <sup>13</sup>        |

#### Figure 2 Pulse detection and analysis

<sup>&</sup>lt;sup>9</sup> Average data rate is trigger rate multiplied with size of data set.

<sup>&</sup>lt;sup>10</sup> Available in FWDAQ and FWPD.

<sup>&</sup>lt;sup>11</sup> The header is 72 bytes.

<sup>&</sup>lt;sup>12</sup> Requires FWPD. Not available in FWDAQ.

<sup>&</sup>lt;sup>13</sup> Each pulse result in 16 bytes of attribute data

# TELEDYNE SP DEVICES Everywhereyoulook™

### 6 CHANGING NUMBER OF CHANNELS

Some hardware models support both one and two channels operation. Changing from two channels to one channel is done by changing firmware image in the FPGA. Both firmware images are stored in the non-volatile memory of the digitizer. Use the software tool ADQAssist to change boot image. Changing firmware requires power cycling of the PC for the PCIe bus to enumerate.

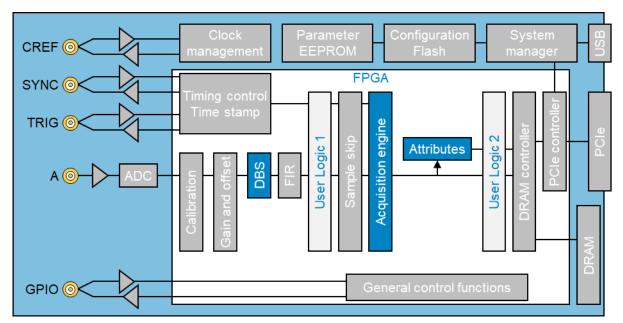

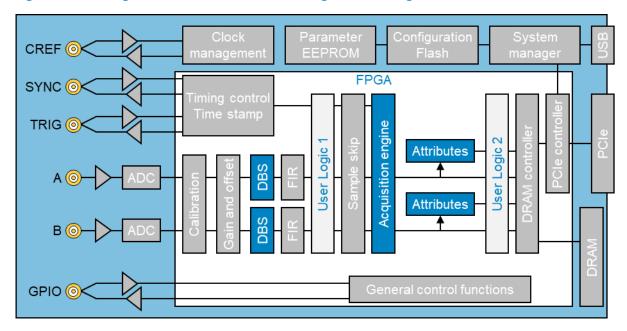

## 7 BLOCK DIAGRAM

Below are block diagrams for FWPD installed in various hardware configurations.

The User Logic 1 and User Logic 2 blocks are available for the user through the Firmware Development Kit, DEVPD, which is ordered separately and available in 2024.

Figure 3 Block diagram for FWPD installed on a single-channel digitizer.

Figure 4 Block diagram for FWPD installed on a dual-channel digitizer.

Figure 5 FWPD combined with PDRX, illustrated with channel combination activated.

Figure 6 Typical digitizer in the ADQ3 family.

# TELEDYNE SP DEVICES Everywhereyoulook™

#### **Important Information**

Teledyne Signal Processing Devices Sweden AB (Teledyne SP Devices) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to Teledyne SP Devices' general terms and conditions supplied at the time of order acknowledgment.

Teledyne SP Devices warrants that each product will be free of defects in materials and workmanship, and conform to specifications set forth in published data sheets, for a period of three (3) years. The warranty commences on the date the product is shipped by Teledyne SP Devices. Teledyne SP Devices' sole liability and responsibility under this warranty is to repair or replace any product which is returned to it by Buyer and which Teledyne SP Devices determines does not conform to the warranty. Product returned to Teledyne SP Devices for warranty service will be shipped to Teledyne SP Devices at Buyer's expense and will be returned to Buyer at Teledyne SP Devices' expense. Teledyne SP Devices will have no obligation under this warranty for any products which (i) has been improperly installed; (ii) has been used other than as recommended in Teledyne SP Devices' installation or operation instructions or specifications; or (iii) has been repaired, altered or modified by entities other than Teledyne SP Devices. The warranty of replacement products shall terminate with the warranty of the product. Buyer shall not return any products for any reason without the prior written authorization of Teledyne SP Devices.

In no event shall Teledyne SP Devices be liable for any damages arising out of or related to this document or the information contained in it.

TELEDYNE SP DEVICES' EXPRESS WARRANTY TO BUYER CONSTITUTES TELEDYNE SP DEVICES' SOLE LIABILITY AND THE BUYER'S SOLE REMEDY WITH RESPECT TO THE PRODUCTS AND IS IN LIEU OF ALL OTHER WARRANTIES, LIABILITIES AND REMEDIES. EXCEPT AS THUS PROVIDED, TELEDYNE SP DEVICES DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING ANY WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT.

TELEDYNE SP DEVICES DOES NOT INDEMNIFY, NOR HOLD THE BUYER HARMLESS, AGAINST ANY LIABILITIES, LOSSES, DAMAGES AND EXPENSES (INCLUDING ATTORNEY'S FEES) RELATING TO ANY CLAIMS WHATSOEVER. IN NO EVENT SHALL TELEDYNE SP DEVICES BE LIABLE FOR SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAMAGES, INCLUDING LOST PROFIT, LOST DATA AND THE LIKE, DUE TO ANY CAUSE WHATSOEVER. NO SUIT OR ACTION SHALL BE BROUGHT AGAINST TELEDYNE SP DEVICES MORE THAN ONE YEAR AFTER THE RELATED CAUSE OF ACTION HAS ACCRUED. IN NO EVENT SHALL THE ACCRUED TOTAL LIABILITY OF TELEDYNE SP DEVICES FROM ANY LAWSUIT, CLAIM, WARRANTY OR INDEMNITY EXCEED THE AGGREGATE SUM PAID TO SP BY BUYER UNDER THE ORDER THAT GIVES RISE TO SUCH LAWSUIT, CLAIM, WARRANTY OR INDEMNITY.

#### Worldwide Sales and Technical Support

www.spdevices.com

#### **Teledyne SP Devices Corporate Headquarters**

Teknikringen 8 SE-583 30 Linköping Sweden Phone: +46 (0)13 465 0600 Fax: +46 (0)13 991 3044 Email: <u>info@spdevices.com</u>

Copyright © 2024 Teledyne Signal Processing Devices Sweden AB. All rights reserved, including those to reproduce this publication or parts thereof in any form without permission in writing from Teledyne SP Devices.